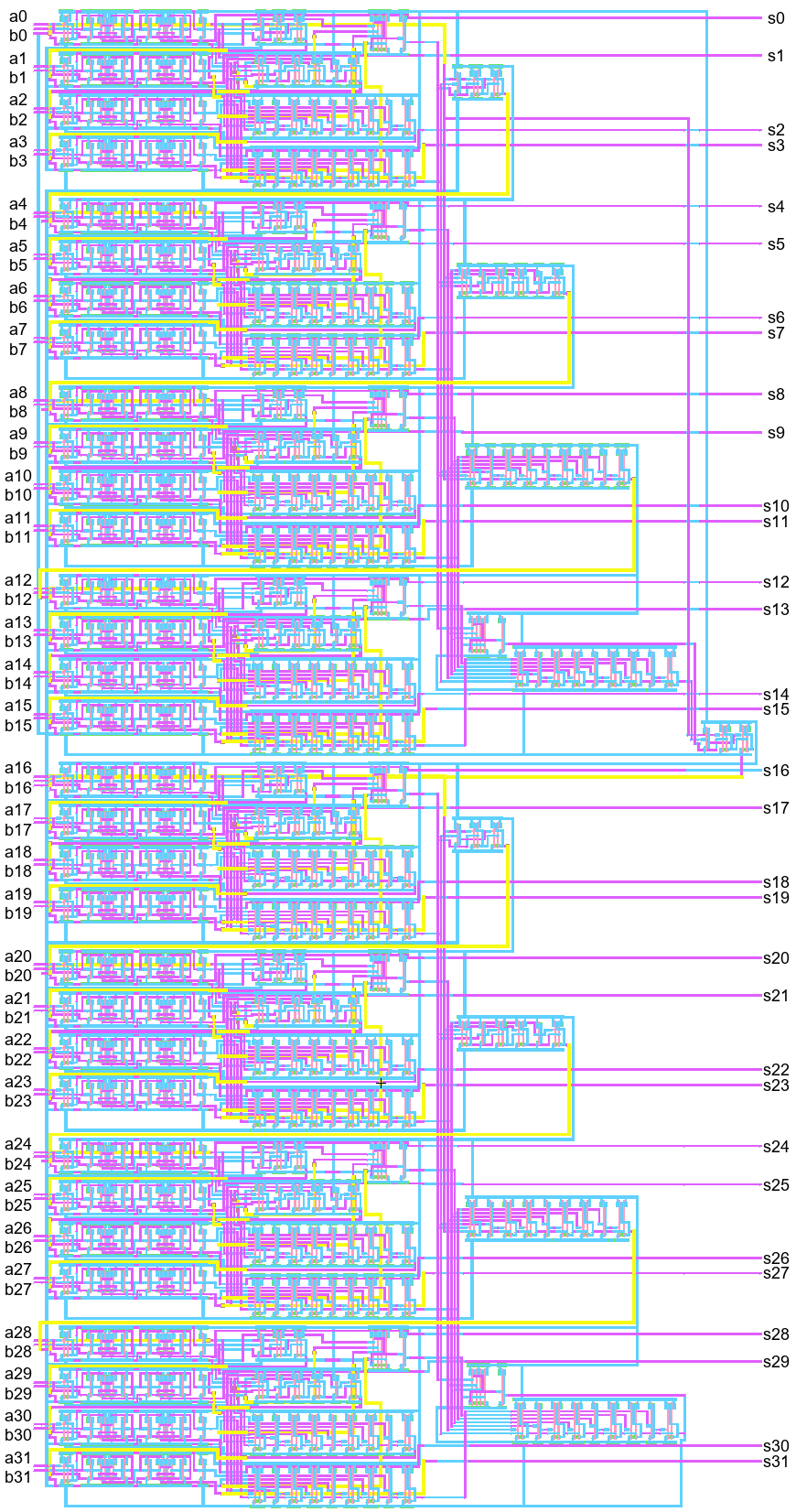

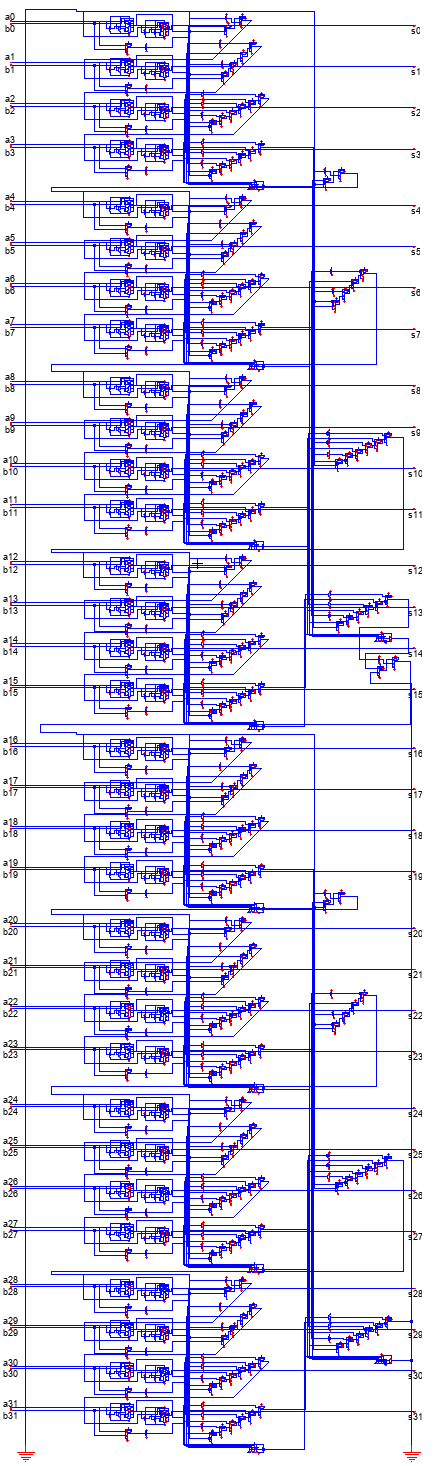

CMOS 32 Bit Carry Lookahead Adder

Project Information

- Category: Circuit

- Project Date: November 2019 - December 2019

- Project URL: https://github.com/ChibiKev/CMOS-CLA-32

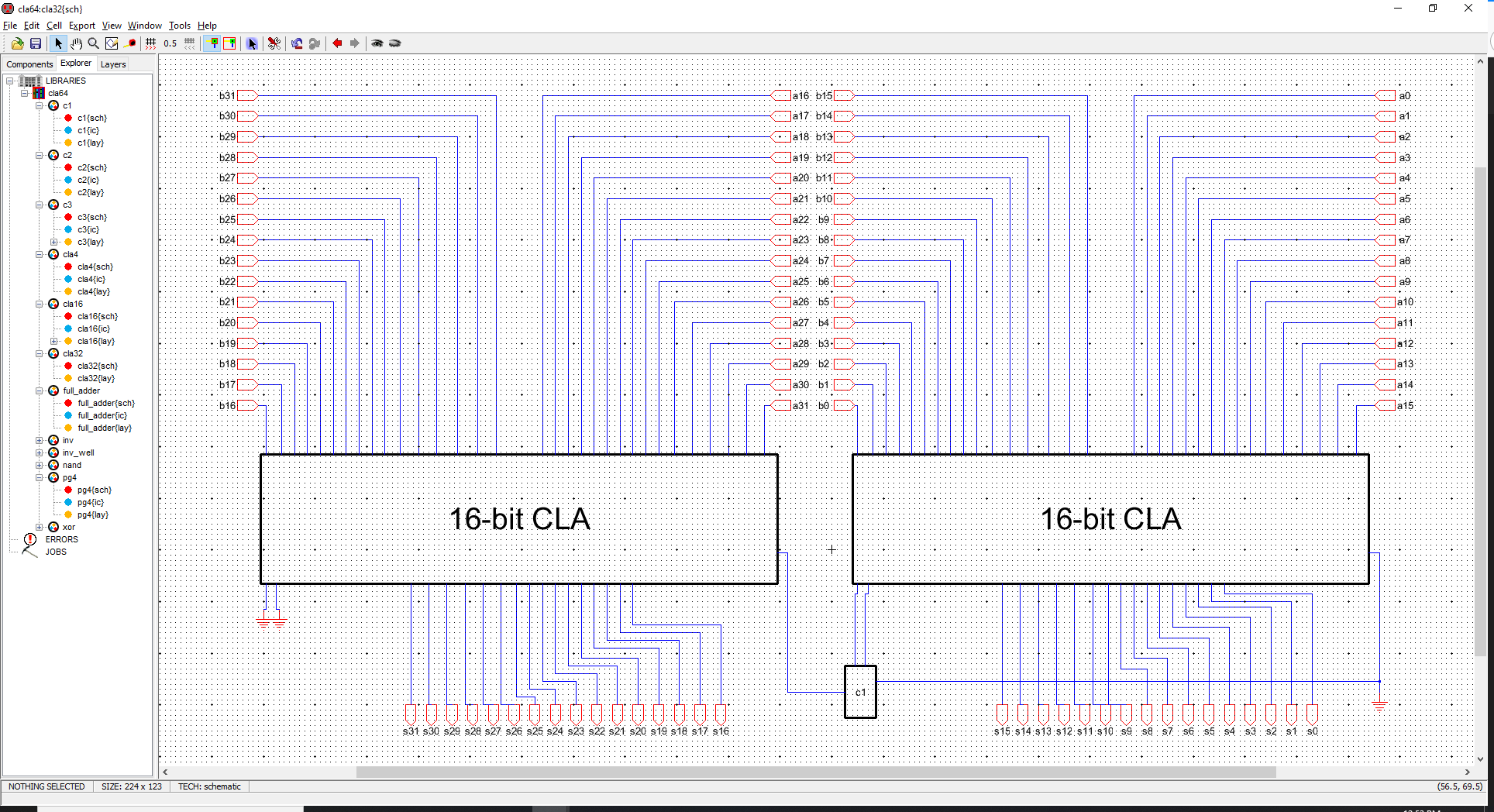

Designed a CMOS of a 32-bit Carry Lookahead Adder (CLA) using Electric.

The purpose of using Carry Lookahead is to enable the circuit to calculate carry-input signals for all full adders at the same time, instead of waiting for the carry-out signal from one full adder to ripple into the next. Because all carry signals are computed at the same time, this enables this circuit to perform binary addition faster than the Ripple-Carry Adder. Here, we see a phenomenon known as the Space-Time tradeoff, where we increase the physical space used by the circuit in order to decrease the time it takes for the circuit to perform its intended function.

To design this, We used old components we designed before: the inverter, NAND gate, XOR gate, and full adder. We modified the full adder to output two signals, propagate (P) and generate (G), as opposed to the carry-out signal. These two signals are used in the Look-Ahead Carry Unit (LCU) modules that will compute the carry-in signals for all full adders in constant time. The constant-time computation of carry-in signals, as opposed to the rippling of them in the Ripple-Carry Adder design, is the essence of the Carry Lookahead Adder.

We then designed C1, C2, and C3 modules that compute the carry-in signals for the latter three full adders. The carry-in signal for the first full adder is inputted directly from outside the circuit. This will realize a four-bit CLA design. But to scale up, we use another C3 module and a four-input AND gate (called the PG4 module) to output propagate and generate signals for the entire four-bit CLA.

We then used the four-bit CLA to build a 16-bit CLA, using four four-bit CLAs and the same LCU modules. We then use the 16-bit CLA to build up once again to the final circuit, the 32-bit Carry Lookahead Adder.

View Report View Presentation